5.直流耦合電路中必須始終考慮1/f噪聲

1/f噪聲對超低頻率電路是一大威脅,因為許多常用噪聲抑制技術,像低通濾波、均值和長時間積分等,對它都無效。然而,許多直流電路的噪聲是以白噪聲源為主,1/f噪聲對總噪聲無貢獻,因而不用計算1/f噪聲。為了弄清這種效應,考慮一個放大器,其1/f噪聲轉折頻率fnc為10 Hz,寬帶噪聲為10 nV/√Hz。對于各種帶寬,計算10秒采集時間內包含和不含1/f噪聲兩種情況下的電路噪聲,以確定不考慮1/f噪聲的影響。當帶寬為fnc的100倍時,寬帶噪聲開始占主導地位;當帶寬超過fnc的1000倍時,1/f噪聲微不足道。現代雙極性放大器可以具有比10 Hz低很多的噪聲轉折頻率,零漂移放大器則幾乎完全消除了1/f噪聲。

表1.1/f噪聲影響與電路帶寬的關系示例

6.因為1/f噪聲隨著頻率降低而提高,所以直流電路具有無限大噪聲

雖然直流對電路分析是一個有用的概念,但真實情況是,如果認為直流是工作在0 Hz,那么實際上并不存在這樣的事情。隨著頻率越來越低,趨近0 Hz,周期會越來越長,趨近無限大。這意味著存在一個可以觀測的最低頻率,哪怕電路在理論上是直流響應。該最低頻率取決于采集時長或孔徑時間,也就是觀測器件輸出的時長。如果一名工程師開啟器件并觀測輸出100秒,則其能夠觀測到的最低頻率偽像將是0.01 Hz。這還意味著,此時可以觀測到的最低頻率噪聲也是0.01 Hz。

現在通過一個數值例子來展開說明,考慮一個DC至1 kHz電路,連續監控其輸出。如果在前100秒觀測到電路中一定量的1/f噪聲,從0.01 Hz至1 kHz(5個十倍頻程的頻率),則在30年(約1 nHz,12個十倍頻程)中觀測到的噪聲量可計算為√12/5 = 1.55,或者說比前100秒觀測到的噪聲多55%。這種增加幾乎沒有任何意義,即使考慮最差情況——1/f噪聲持續增加到1 nHz(目前尚無測量證據)——也是如此。理論上,如果沒有明確定義孔徑時間,1/f噪聲可以計算到一個等于電路壽命倒數的頻率。實踐中,電路在如此長時間內的偏差以老化效應和長期漂移為主,而不是1/f噪聲。許多工程師為直流電路的噪聲計算設定0.01 Hz或1 mHz之類的最低頻率,以使計算切合實際。

7.噪聲等效帶寬會使噪聲倍增

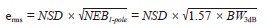

噪聲等效帶寬(NEB)對噪聲計算是一個很有用的簡化。由于截止頻率以上的增益不是0,某些超出電路帶寬的噪聲會進入電路中。NEB是計算的理想磚墻濾波器的截止頻率,它會放入與實際電路相同的噪聲量。NEB大于–3 dB帶寬,已針對常用濾波器類型和階數進行計算,例如:對于單極點低通濾波器,它是–3 dB帶寬的1.57倍,寫成公式就是NEB1-pole = 1.57 × BW3dB。然而,關于應把該乘法因數放在噪聲公式中的何處,似乎一直存在混淆。請記住,NEB調節的是帶寬,而非噪聲,因此應在根號下面,如下式所示:

8.電壓噪聲最低的放大器是最佳選擇

選擇運算放大器時,電壓噪聲常常是設計人員唯一考慮的噪聲規格。其實電流噪聲同樣不能忽略。除非在有輸入偏置電流補償等特殊情況下,電流噪聲通常是輸入偏置電流的散粒噪聲:in = √2 × q × IB。電流噪聲通過源電阻轉換為電壓,因此,如果放大器輸入端前面有一個大電阻,那么電流噪聲對系統噪聲的貢獻可能大于電壓噪聲。電流噪聲會成為問題的典型情況是使用低噪聲運算放大器且其輸入端串聯一個大電阻時。例如,考慮低噪聲運算放大器ADA4898-1,其輸入端串聯一個10 kΩ電阻。ADA4898-1的電壓噪聲為0.9 nV/√Hz,10 kΩ電阻的噪聲為12.8 nV/√Hz,2.4 pA/√Hz電流噪聲乘以10 kΩ電阻等于24 nV/√Hz,這是系統中的最大噪聲源。在類似這種電流噪聲占主導地位的情況下,常常可以找到電流噪聲較低的器件,從而降低系統噪聲;對精密放大器尤其如此,不過高速FET輸入運算放大器對高速電路也可能有幫助。例如,若不選擇ADA4898-1(從而得不到電壓噪聲低至0.9 nV/√Hz的好處),可以選擇AD8033或ADA4817-1等JFET輸入放大器。

9.在第一級提供大部分增益可實現最佳噪聲性能

為了實現更好的噪聲性能,常常建議在第一級提供增益,這是對的,因為信號會比隨后各級的噪聲要大。然而,這樣做的缺點是會削弱系統能夠支持的最大信號。某些情況下,與其在第一級提供很大一部分增益(雖然這樣可以提高測量靈敏度,但會限制動態范圍),不如限制第一級提供的增益,并用高分辨率進行數字化處理,使靈敏度和動態范圍都達到最大。

10.給定阻值時,所有類型電阻的噪聲相同

電阻的約翰遜噪聲非常重要,以至于我們需要一個簡單的公式來計算某一電阻在某一溫度下的噪聲。然而,約翰遜噪聲是電阻中可以觀測到的最小噪聲,而且并非所有類型的電阻都有同等噪聲。還有過量噪聲,它是電阻中1/f噪聲的來源之一,與電阻類型密切相關。過量噪聲(有時候也誤稱為電流噪聲)與電流在非連續介質中流動的方式有關。它被規定為噪聲指數(NI),單位為dB,以每十倍頻程1 μV rms/Vdc為基準。這意味著:如果一個0 dB NI的電阻上有1 Vdc電壓,則給定十倍頻程時的過量噪聲為1 μV rms。碳和厚膜電阻的NI最高,可能高達+10 dB左右,在信號路徑的噪聲敏感部分中最好避免使用。薄膜電阻一般要好得多,約為–20 dB;金屬箔和繞線電阻可以低于–40 dB。

11.給定足夠長的采集時間,均值法可將噪聲降至無限小

一般認為均值法可將噪聲降低均值數的平方根倍。這在一定條件下是成立的,即NSD必須保持平坦。然而,在1/f范圍內和其他幾種情況下,這種關系不成立。考慮在一個以恒定頻率fs采樣的系統中使用均值法,對n個樣本求均值并進行1/n抽取,返回m個抽取樣本。取n個平均值會將抽取后的有效采樣速率變為fs/n,系統看到的有效最大頻率降低n倍,白噪聲降低√n倍。然而,獲得m個樣本的時間也會延長n倍,因此系統可以看到的最低頻率也會降低n倍(記住,沒有0 Hz這種事)。取的均值數越多,頻段上的這些最大和最小頻率就越往下移。一旦最大和最小頻率均在1/f范圍內,總噪聲便僅取決于這些頻率之比,再提高均值數對降低噪聲沒有進一步的好處。同樣的道理也適用于多斜率等積分ADC的長積分時間。除了數學上的限制以外,還存在其他實際限制。例如,若量化噪聲是主要噪聲源,使得直流輸入電壓下的ADC輸出為一個無閃爍的恒定碼,則任何數量的均值都會返回同一個碼 。